Altera Quartus II v13.0 全球最快FPGA設(shè)計(jì)的實(shí)現(xiàn)利器

隨著電子技術(shù)的快速發(fā)展,現(xiàn)場可編程門陣列(FPGA)設(shè)計(jì)在通信、數(shù)據(jù)中心和嵌入式系統(tǒng)中扮演著關(guān)鍵角色。Altera Quartus II軟件v13.0版本的發(fā)布,標(biāo)志著FPGA設(shè)計(jì)工具的新里程碑,它通過優(yōu)化編譯算法和集成先進(jìn)功能,顯著提升了設(shè)計(jì)性能,被譽(yù)為支持實(shí)現(xiàn)世界上最快的FPGA設(shè)計(jì)的工具。該軟件不僅適用于FPGA開發(fā),還擴(kuò)展到了ASIC技術(shù)領(lǐng)域,為電子發(fā)燒友和工程師們提供了強(qiáng)大的開發(fā)平臺(tái)。

Quartus II v13.0在性能優(yōu)化方面取得了顯著突破。它引入了增強(qiáng)的時(shí)間收斂技術(shù)和并行編譯功能,能夠大幅縮短設(shè)計(jì)周期,同時(shí)提高時(shí)鐘頻率和降低功耗。例如,通過改進(jìn)的布局和布線算法,該軟件能夠自動(dòng)優(yōu)化關(guān)鍵路徑,確保設(shè)計(jì)在高速運(yùn)行時(shí)保持穩(wěn)定。v13.0版本還加入了對最新FPGA器件的支持,如Stratix V系列,這些器件在吞吐量和能效方面處于行業(yè)領(lǐng)先地位。

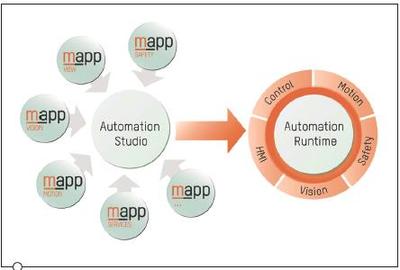

在易用性和集成性方面,Quartus II v13.0同樣表現(xiàn)出色。它提供了直觀的圖形用戶界面和豐富的IP核庫,使得開發(fā)者能夠快速構(gòu)建復(fù)雜系統(tǒng)。軟件還加強(qiáng)了與硬件仿真和驗(yàn)證工具的集成,如ModelSim和SignalTap II邏輯分析儀,這有助于在早期階段發(fā)現(xiàn)并修復(fù)設(shè)計(jì)錯(cuò)誤。它支持多種設(shè)計(jì)輸入方式,包括VHDL、Verilog和SystemVerilog,方便不同背景的工程師靈活使用。

從應(yīng)用角度來看,Quartus II v13.0在通信、工業(yè)自動(dòng)化和消費(fèi)電子等領(lǐng)域展現(xiàn)出巨大潛力。例如,在5G通信系統(tǒng)中,它可以用于實(shí)現(xiàn)高速數(shù)據(jù)處理的FPGA設(shè)計(jì),從而提升網(wǎng)絡(luò)性能。對于電子發(fā)燒友社區(qū),該軟件提供了免費(fèi)的網(wǎng)絡(luò)版,降低了學(xué)習(xí)和實(shí)驗(yàn)的門檻,鼓勵(lì)更多人參與到FPGA/ASIC技術(shù)的創(chuàng)新中。

Altera Quartus II v13.0不僅是一款高效的開發(fā)工具,更是推動(dòng)FPGA技術(shù)前沿的重要力量。通過持續(xù)的技術(shù)迭代和社區(qū)支持,它將繼續(xù)引領(lǐng)電子設(shè)計(jì)自動(dòng)化的發(fā)展,助力工程師們實(shí)現(xiàn)更快、更可靠的系統(tǒng)設(shè)計(jì)。

如若轉(zhuǎn)載,請注明出處:http://www.clpengineering.org.cn/product/35.html

更新時(shí)間:2026-02-24 15:15:55